参数提取是只指经过布局布线,再经过版图设计之后,根据工艺特点与参数,提取出包含描述各种线上电阻、电容以及寄生电阻电容的网表文件。提取出的网表文件既可以作为LVS检查中的版图信息文件,也可以用来进行后仿真。

特征尺寸随摩尔定律下降,在大规模集成电路设计中,互连线上的延时/电阻、电容已经越来越成为影响系统性能的重要参数。连线的延时越来越决定了系统的最高频率;互连线的电阻、功耗越来越影响系统功耗;互连线间的耦合电容还会造成信号完整性问题。

从一维到二维到三维的寄生参数

作为传统的提取方式,一维(1-D)提取在CMOS进入深亚微米之前一直是主流的提取方式。如图1,连线至衬底电容的面电容、连线边墙至衬底的边缘电容等。

图1 一维提取

当CMOS工艺深入深亚微米之后,工艺特征尺寸越来越小,在布局布线时,连线与连线之间的距离变得越来越小,只考虑垂直方向的寄生参数就不能精确的反映电路的实际性能。二维提取不仅提取垂直方向上的面电容,还会提取水平方向的连线间的寄生电容。

如图2所示,当连线尺寸不断减小时,连线与衬底之间的寄生电容会减小,同时连线之间的寄生电容随着距离减小而呈现倒数关系的增加。

图2 二维提取

另外,如图3,随着工艺层次的不断复杂,不同层次间的寄生电容同样占据了越来越重要的部分。

图3 2.5维提取

现在先进工艺中越来越使用三维提取来提高寄生参数提取的精度。基本原理是使用泊松方程以及拉普拉斯方程等空间基本方程对根据版图建立的三维空间里的版图连线长度。驱动能力和负载进行计算机CAD模拟,从而得到最为精确_的模拟数据。不过工作量和计算量很大。

图3 三维提取

静电场的泊松方程和拉普拉斯方程 若空间分区充满各向同性、线性、均匀的媒质,则从静电场强与电势梯度的关系E=-墷V和高斯定理微分式,即可导出静电场的泊松方程:

式中ρ为自由电荷密度,纯数εr为各分区媒质的相对介电常数,真空介电常数εo=8.854×10-12法/米。在没有自由电荷的区域里,ρ=0,泊松方程就简化为拉普拉斯方程

StarRC中各个文件的作用

图4 RC提取的输入件

三家EDA寄生参数抽取工具,分别是StarRC(synopsys), XRC(Mentor),QRC(Cadence),其中QRC现在有个升级版本Quantus,但是由于calibre在DRC 和LVS方面太强,所以一般都会提供calibre LVS + StarRC 或者QRC的flow。

starRC rule 都会提供如下的文件:1、calibre LVS rule;2 、itf file(option);3、map file ;4、query;5、xxx.nxtgrd;6、xxx.layermap。

第一个lvs 文件是在run RC前需要给StarRC 产生的database,这里一般会产生一个CCI(Calibre Connectivity interface)的database,所以一般也叫CCI flow。QCI 为(Quantus Connectivity Interface)。

第二个itf 文件,是StarRC的工艺描述文件,描述需要抽RC的layer以及介质层,主要是各种工艺参数,这个有可能fab不给你,那后面如果要转model 就需要多一步。这个工艺描述文件在starRC里就是这个itf文件,而在XRC里叫mipt 文件。

第三个map_file是将layoutdatabase(ndm/def、lef等)层次与nxtgrd的层次形成映射关系。

后面三个是run StarRC的必要文件,其中nxtgrd 就是用itf 产生的model文件,类似于XRC中的rules.R 和 rules.C。

如果fab没有nxtgrd就用itf来转一个,具体命令如下:grdgenxo ****.itf。

另外还需要design的def/lef作为输入件。gds可以添加metal fill信息,抽取更精准。

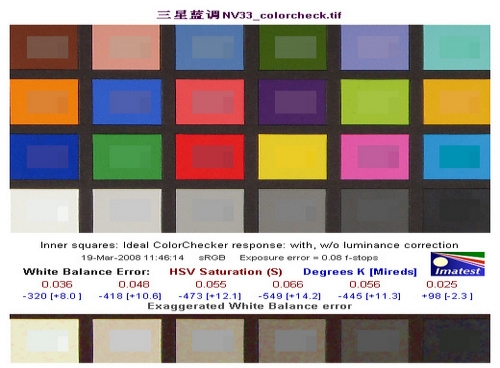

Captable和QRC tech file

RC抽取的过程需要用到工艺文件,一般会有以下几种:

Cadence Synopsys

ict <---> itf、 process file

captable<---> tluplus、 rc model for APR tools

qrcTechfile <---> nxtgrd、 rc model for stand alone RC Ext. tools

captable由ict文件生成,其内容主要是电容电阻的查表。通常由半导体厂提供。

因为ict文件是工艺参数,并不是直接的电阻电容值,如果直接使用,则每一段导线都要根据工艺参数去计算电阻电容,计算量太大。所以,为了减少RC抽取过程中的计算量,节省RC抽取的时间,将ict文件转换成captable。在captable中,由导线的长度和宽度查表即可得到电阻电容值,虽然过程中也要计算一些系数的影响(比如温度系数),但计算量仍然大幅减少了。由此可见,captable的生成过程就是由ict中的工艺参数按照一些特定的导线尺寸计算出相应电阻电容值的过程。生成时间在1~2天的量级。

captable用以下命令生成:generateCapTbl

该命令既可以在Encounter中执行(支持多线程/CPU);也可以单独运行(不支持多线程/CPU)。命令用法详见:Encounter Text Command Reference

captable的精度低于后文所讲的qrcTechfile,主要用于布线之前的步骤。何种阶段使用何种RC抽取引擎要在精度和运行时间之间进行折中。因为布线之前的步骤均使用预布线(trial route),所以没有必要使用qrcTechFile。

captable的详细介绍请参考:Encounter User Guide --> RC Extraction一章

qrcTechfile也由ict文件生成,用于QRC引擎。通常由半导体厂提供。

其原理与captable相同,但对导线的3D建模更加精确,并且会考虑更多的工艺效应,所以其电阻电容值也更加精确。相应的,qrcTechfile的生成非常耗时,通常在10天的量级。qrcTechfile用以下命令生成:Techgen。这是一个小工具,可以在Encounter的安装目录下找到。具体用法请参考:QRC Techgen Reference Manual ,QRC引擎是具有signoff质量的RC抽取工具,一般从routing开始就应该使用QRC引擎进行RC抽取,以获得较高的精度,加速时序收敛。

图6 qrc的输入件

本文第三小节QRC tech file部分来自如下链接,原作者博客暂时打不开,所以标注不了作者名字:

https://blog.csdn.net/weixin_42099269/article/details/119854858 ;

https://blog.sina.com.cn/s/blog_6c090c5d0101aq1r.html